Copy Link

Add to Bookmark

Report

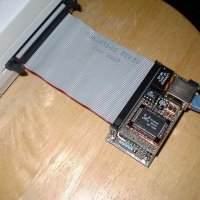

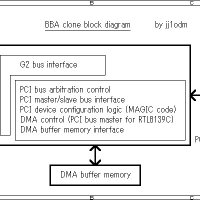

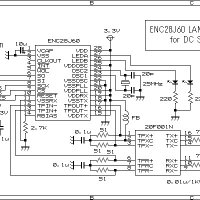

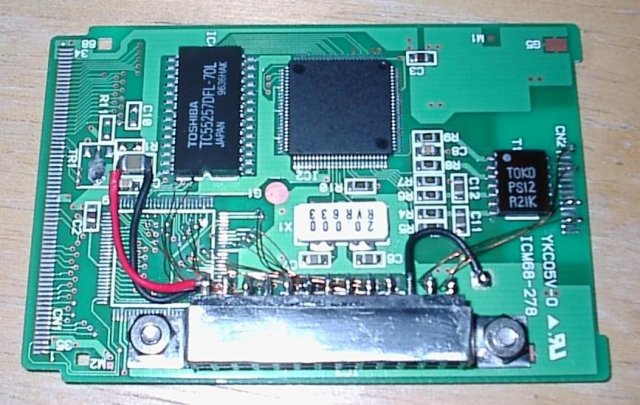

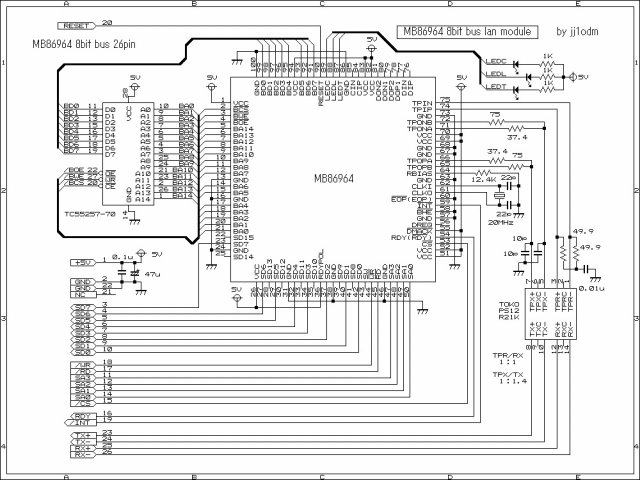

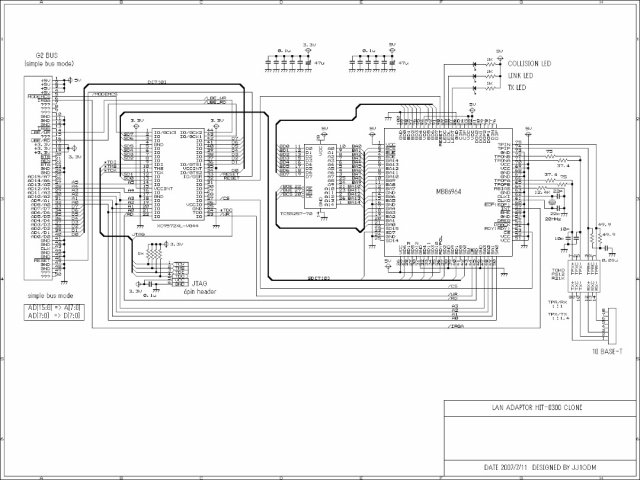

Dreamcast design example: LAN Adapter HIT-0300 clone (use MB86964) (part 3)

The original article, written by jj1odm, is available at http://jj1odm.sizious.com/

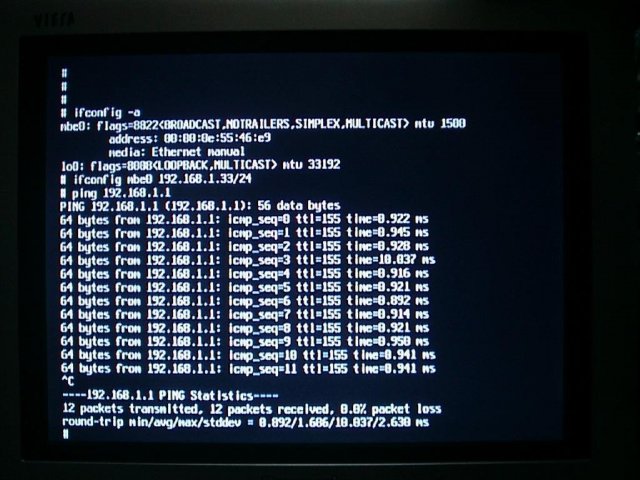

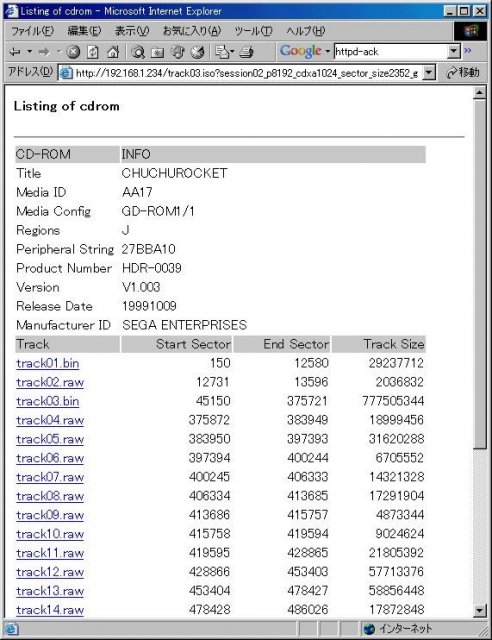

Verification software:

IP-upload 1.0.4

KOS 1.1.9 network samples

NetBSD 3.1

httpd-ack (v20070720) (It is necessary to set ISP by using BBA.)

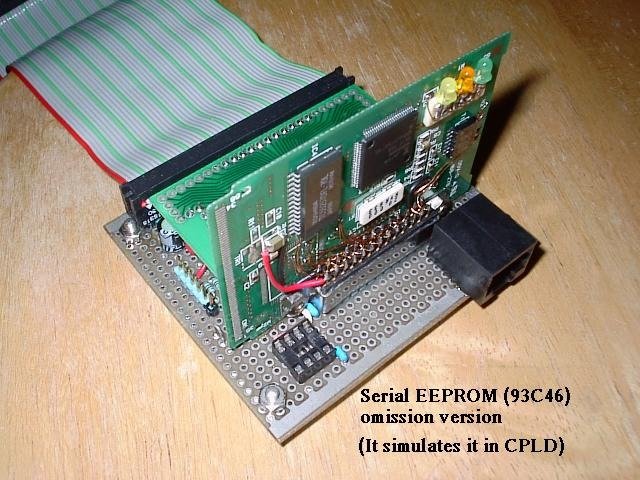

Serial EEPROM omission version:

93C46 is simulated in CPLD.

(The MAC address is MAC_WORD_0/MAC_WORD_1/MAC_WORD_2 in the verilog source code. )

cpld source:

hit0300_clonex.v

// $$$ : hit0300_clonex.v -- lan adaptor HIT-0300 clone (use MB86964 and serial eeprom simulation).

//

// used device:

// XC9572XL-5-VQ44 - G2 bus (simple bus mode) interface

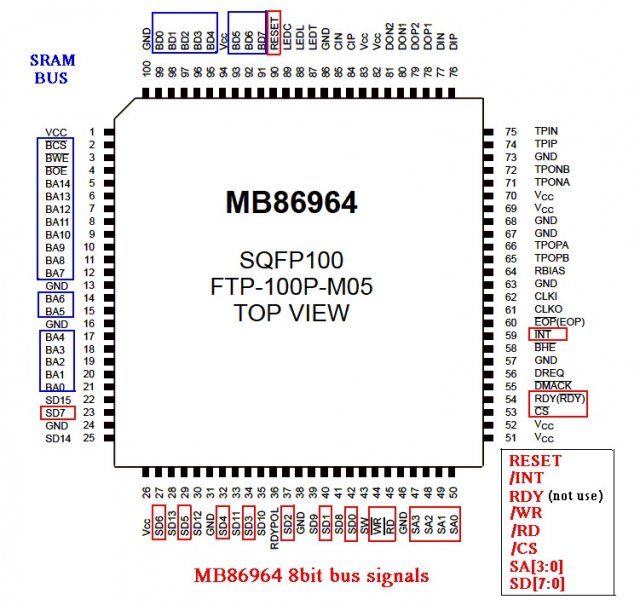

// MB86964 - lan controller (an original lan adaptor uses MB86967)

// TC55257DFL-70L - buffer SRAM 32kbytes

//

// device address mapping:

// 0xa0600400 - 0xa060043c: (long word alignment) MB86964 lan controller device

// (change DLCR7 register ID code. MB86964{'01'} => MB86967{'10'})

// 0xa0600440: EEPROM control port {EECS/EESK} (for MB86967 compatibility)

// serial eeprom simulation

// 0xa0600444: EEPROM data in/out port {EEDO/EEDI} (for MB86967 compatibility)

// serial eeprom simulation

// 0xa0600480: reset port register

//

// date 2007/7/11 designed by jj1odm

//

// add serial eeprom simulation:

// support read command only

// change your mac address constant (MAC_WORD_0/MAC_WORD_1/MAC_WORD_2)

//

// last update 2007/7/25

`timescale 1ns / 1ps

module hit0300_clonex(

input modemcsn, // G2 bus modem area enable {simple bus mode} (activ low)

input lben_wrn, // G2 bus write strobe {simple bus mode} (active low)

input uben_rdn, // G2 bus read strobe {simple bus mode} (activ low)

inout [7:0] d, // G2 bus data bus {simple bus mode} (ad[7:0] 8bit data bus)

input [5:0] a, // G2 bus address bus {simple bus mode} (ad[15:8] 8bit adr. bus / use 6bit(ad[13:8]))

input resetn, // G2 bus system reset (active low)

output csn, // MB86964 chip select (active low)

output rdn, // MB86964 read strobe (active low)

output wrn, // MB86964 write strobe (active low)

inout [7:0] sd, // MB86964 data bus (8 bit)

output reset // MB86964 chip reset (active high)

);

// change your mac address (ex. 01:23:45:67:89:ab)

parameter MAC_WORD_0 = 16'h0123; // mac word 0 data

parameter MAC_WORD_1 = 16'h4567; // mac word 1 data

parameter MAC_WORD_2 = 16'h89ab; // mac word 2 data

parameter MB86967_ID = 2'b10; // MB86967 ID code

parameter DLCR7_REG = 4'b0111; // MB86964 DLCR7 register (ID code bit[7:6])

parameter EEPORT_REG = 6'b010000; // eeprom control register

parameter EEDIO_REG = 6'b010001; // eeprom data input/output register

parameter RESET_REG = 6'b100000; // reset port register

parameter EE_READ_CMD = 2'b10; // eeprom read command

parameter EE_IDLE_STATE = 1'b0; // eeprom idle state

parameter EE_CMD_STATE = 1'b1; // eeprom command state

reg [7:0] dreg; // for g2 bus

reg [7:0] eeport_reg; // eeprom control port register

reg eedi_reg; // eeprom data in (output) register

reg reset_reg; // reset port register

reg eestate_reg; // eeprom state register

reg [3:0] ee_cnt; // eeprom work counter

reg [7:0] eecmd_reg; // eeprom command register

reg [15:0] eeread_reg; // eeprom read data register

assign csn = ~(~modemcsn & (a[5:4] == 2'b00)); // MB86964 chip select

assign rdn = ~(~csn & ~uben_rdn); // MB86964 read strobe

assign wrn = ~(~csn & ~lben_wrn); // MB86964 write strobe

assign reset = ~resetn | reset_reg; // MB86964 chip reset

assign sd = (~csn & rdn) ? d : 8'hzz;

assign d = dreg;

always @(uben_rdn or modemcsn or a or sd or d or eeport_reg or eedi_reg or eeread_reg[15] or reset_reg) begin

if (~modemcsn & ~uben_rdn) begin // read

if (a[5:4] == 2'b00) begin // read MB86964 registers

dreg < = (a[3:0] == DLCR7_REG) ? {MB86967_ID, sd[5:0]} : sd; // ID code change MB86964 => MB86967

end

else begin // read etc. control registers

case (a)

EEPORT_REG: dreg < = eeport_reg;

EEDIO_REG: dreg < = {eeread_reg[15], 7'b0000000};

RESET_REG: dreg < = {7'b0000000, reset_reg};

default: dreg < = 8'hzz;

endcase

end

end

else dreg < = 8'hzz;

end

always @(posedge lben_wrn or negedge resetn) begin

if (~resetn) begin

eeport_reg < = 8'h00;

eedi_reg < = 1'b0;

reset_reg < = 1'b0;

end

else begin

if (~modemcsn) begin

case (a)

EEPORT_REG: eeport_reg < = d;

EEDIO_REG: eedi_reg < = d[7];

RESET_REG: reset_reg < = d[0];

endcase

end

end

end

// serial eeprom simulation (read command only)

always @(posedge eeport_reg[6]) begin // EESK

if (~eeport_reg[5]) begin // EECS (low then reset)

eestate_reg < = EE_IDLE_STATE;

end

else begin

if (eestate_reg == EE_IDLE_STATE) begin

if (eedi_reg) begin // EEDI (high then EE_CMD_STATE)

eestate_reg < = EE_CMD_STATE;

ee_cnt < = 4'b0000;

end

else begin // shift read data

eeread_reg < = {eeread_reg[14:0], 1'b0}; // EEDO (eeread_reg[15])

end

end

if (eestate_reg == EE_CMD_STATE) begin

if (ee_cnt == 4'b1000) begin

if (eecmd_reg[7:6] == EE_READ_CMD) begin

case (eecmd_reg[5:0]) // eeprom address

0: eeread_reg < = MAC_WORD_0;

1: eeread_reg < = MAC_WORD_1;

2: eeread_reg < = MAC_WORD_2;

default: eeread_reg < = 16'hffff;

endcase

end

eestate_reg < = EE_IDLE_STATE;

end

else begin // shift command data

eecmd_reg < = {eecmd_reg[6:0], eedi_reg}; // EEDI

ee_cnt < = ee_cnt + 4'b0001;

end

end

end

end

endmodule

// end of : hit0300_clonex.v

cpld pin

hit0300_clonex.ucf

#PACE: Start of Constraints generated by PACE

#PACE: Start of PACE I/O Pin Assignments

NET "a< 0>" LOC = "P21" ;

NET "a< 1>" LOC = "P20" ;

NET "a< 2>" LOC = "P19" ;

NET "a< 3>" LOC = "P18" ;

NET "a< 4>" LOC = "P16" ;

NET "a< 5>" LOC = "P14" ;

NET "d< 0>" LOC = "P34" ;

NET "d< 1>" LOC = "P36" ;

NET "d< 2>" LOC = "P37" ;

NET "d< 3>" LOC = "P38" ;

NET "d< 4>" LOC = "P39" ;

NET "d< 5>" LOC = "P40" ;

NET "d< 6>" LOC = "P41" ;

NET "d< 7>" LOC = "P42" ;

NET "csn" LOC = "P27" ;

#NET "eecs" LOC = "P31" ;

#NET "eesk" LOC = "P30" ;

#NET "eedi" LOC = "P29" ;

#NET "eedo" LOC = "P28" ;

NET "lben_wrn" LOC = "P44" ;

NET "modemcsn" LOC = "P1" ;

NET "rdn" LOC = "P22" ;

NET "reset" LOC = "P32" ;

NET "resetn" LOC = "P33" ;

NET "sd< 0>" LOC = "P13" ;

NET "sd< 1>" LOC = "P12" ;

NET "sd< 2>" LOC = "P8" ;

NET "sd< 3>" LOC = "P7" ;

NET "sd< 4>" LOC = "P6" ;

NET "sd< 5>" LOC = "P5" ;

NET "sd< 6>" LOC = "P3" ;

NET "sd< 7>" LOC = "P2" ;

NET "uben_rdn" LOC = "P43" ;

NET "wrn" LOC = "P23" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE